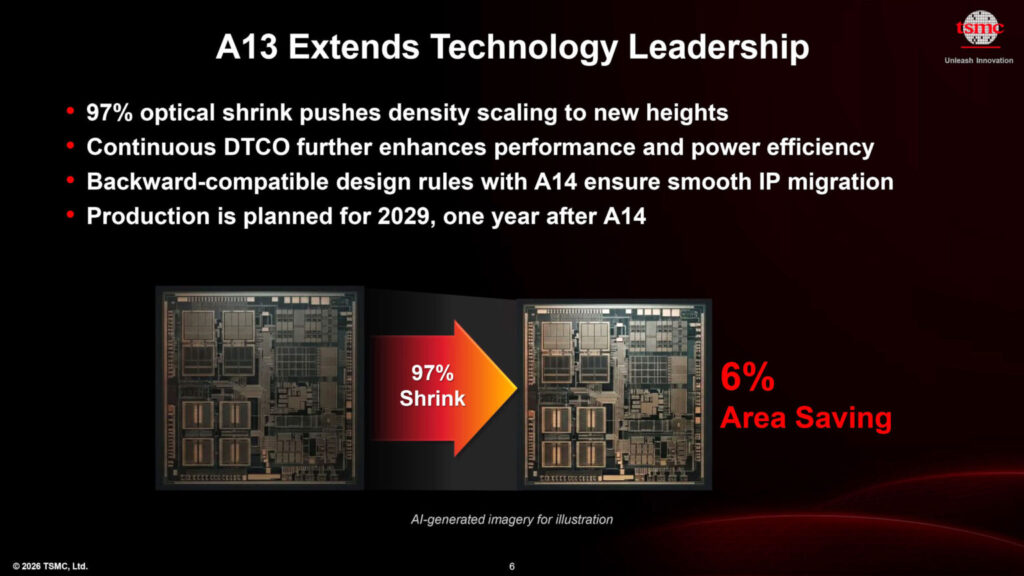

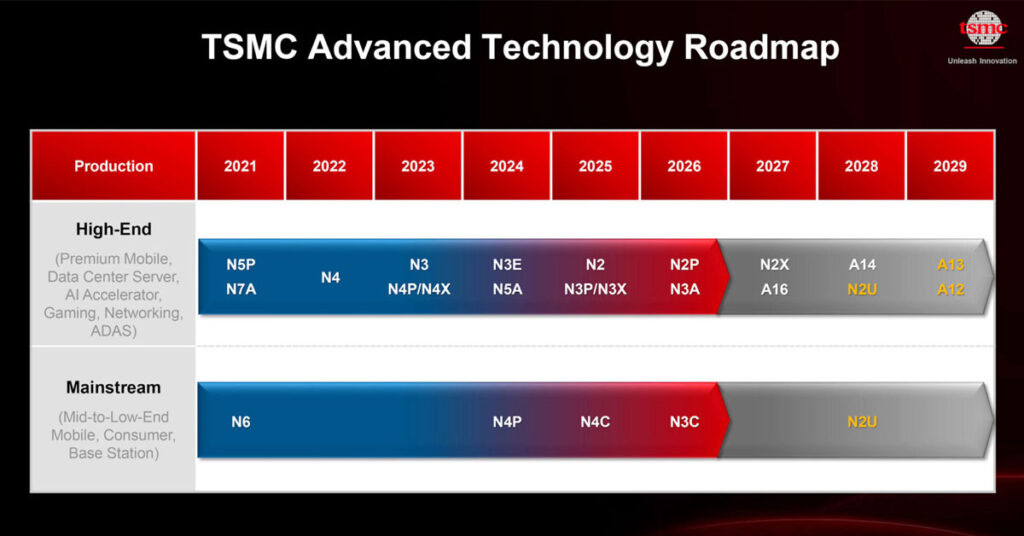

TSMC anuncia el nodo A13: 6% menos área que A14 y producción en 2029

El roadmap de TSMC tomó forma esta semana en el simposio tecnológico de Norteamérica celebrado en Santa Clara. Entre los anuncios, el que más llama la atención para el segmento de semiconductores avanzados es A13: un shrink directo de A14 que promete 6% de reducción de área, compatibilidad total con las reglas de diseño existentes y mejoras adicionales de rendimiento y eficiencia energética vía optimización de diseño y tecnología.

Un paso calculado: shrink sin romper compatibilidad

A13 no reinventa la rueda. Al conservar la compatibilidad con las reglas de diseño de A14, TSMC le da a sus clientes un camino de migración sin necesidad de rediseñar desde cero, algo especialmente valioso para los grandes fabricantes de chips de AI y HPC que ya estarán invirtiendo en A14. La producción de A13 está programada para 2029, un año después de que A14 entre en volumen.

A12 y N2U completan el panorama 2028-2029

En paralelo, TSMC adelantó dos nodos más. A12 funciona como una mejora de la plataforma A14 e incorpora la tecnología Super Power Rail, que entrega energía por la parte trasera del die —una ventaja directa para cargas de trabajo de inteligencia artificial y HPC— con producción también apuntando a 2029. Por su lado, N2U extiende la familia de 2 nm: según TSMC, este nodo logra entre 3% y 4% más velocidad o bien 8% a 10% menos consumo frente a N2P, más una ganancia de densidad lógica de 1.02x a 1.03x. Su producción está prevista para 2028.

CoWoS se expande: de 5,5 a 14 reticles y más allá

TSMC también actualizó su hoja de ruta de empaquetado avanzado. Actualmente produce CoWoS de 5,5 reticles y tiene previsto llevar esa cifra a 14 reticles en 2028, capacidad suficiente para integrar alrededor de 10 dies de cómputo y 20 pilas HBM. Para 2029, todo apunta a que se superará ese límite junto con la plataforma SoW-X de 40 reticles. Ese mismo año está previsto el stacking A14-sobre-A14 SoIC, con una densidad de interconexión 1,8 veces superior a la del SoIC N2-sobre-N2.

El evento también incluyó anuncios en óptica, automoción y procesos de especialidad. La solución de óptica co-empaquetada COUPE entra en producción en 2026 con eficiencia energética 2x superior y latencia 10x menor que los diseños de placa tradicionales. Para automoción, N2A debuta como el primer proceso de nanohoja con certificación automotriz de TSMC, con ganancias de velocidad de 15% a 20% frente a N3A al mismo consumo, apuntando a certificación AEC-Q100 en 2028. El proceso N16HV, para drivers de pantalla, entra en producción este mismo año.

Fuente: VideoCardz